|

1151| 2

|

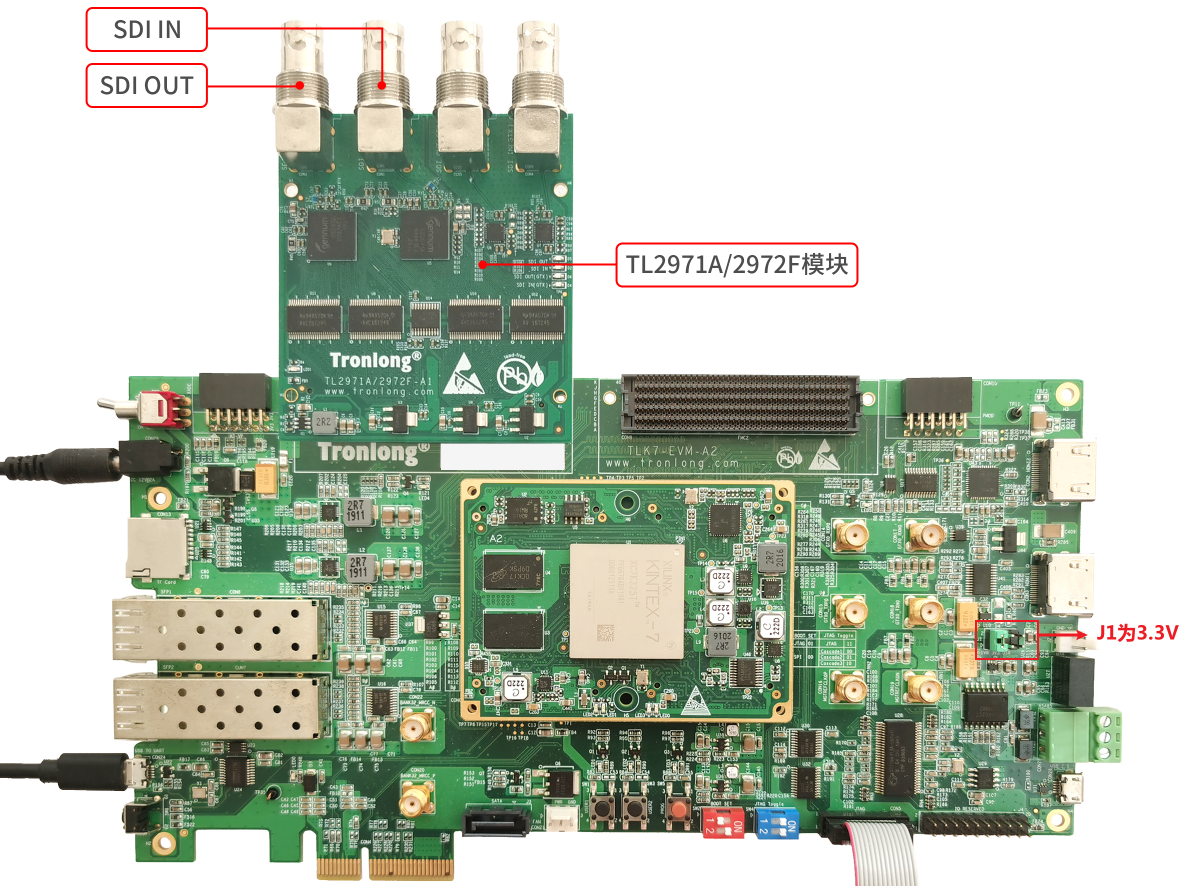

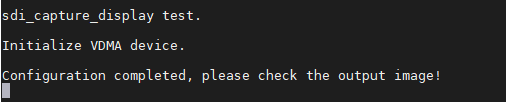

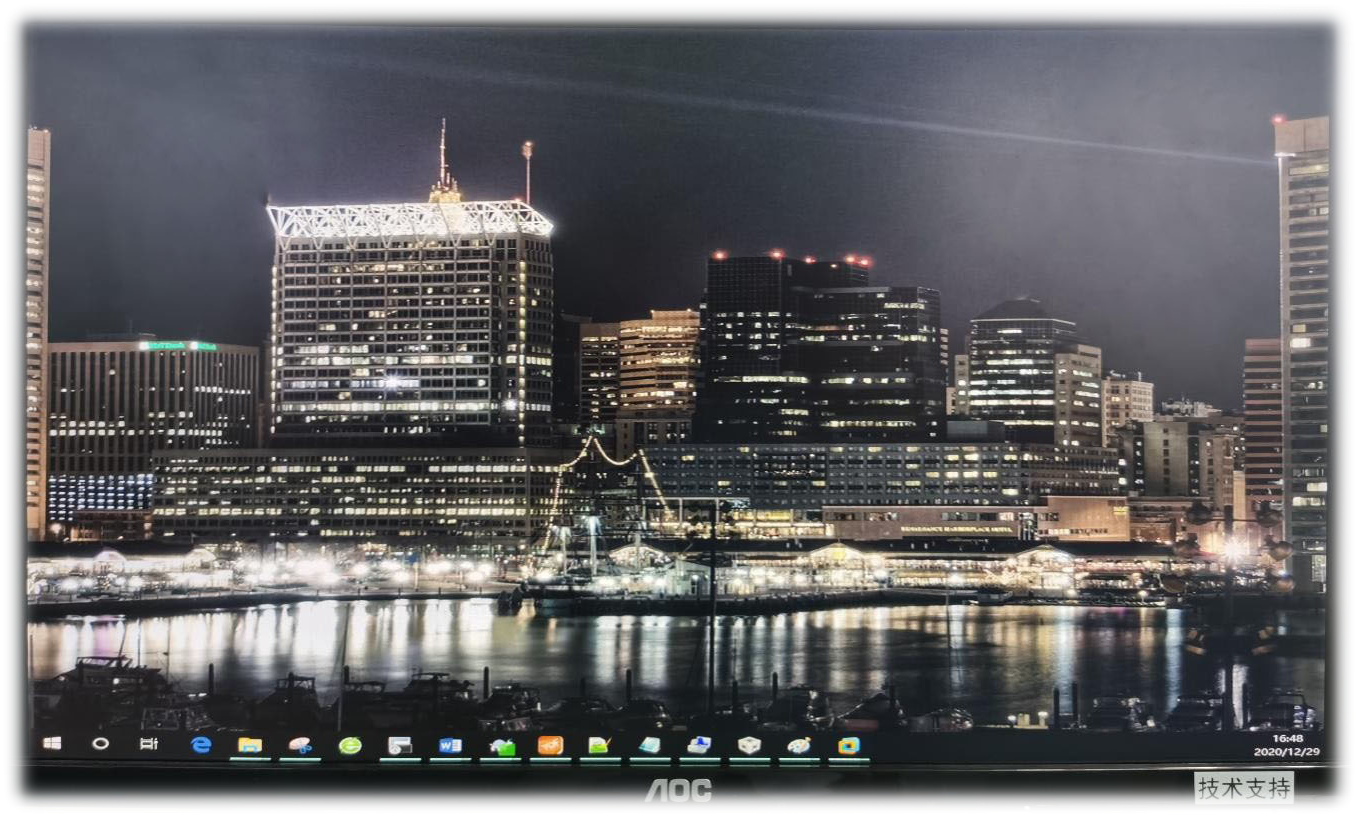

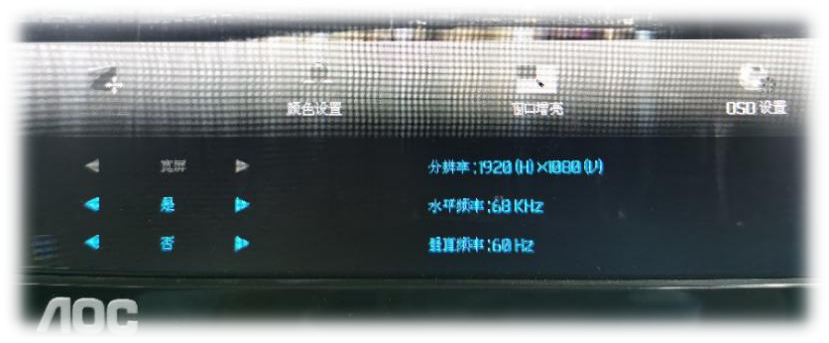

[经验] Kintex-7开发板如何实现FPGA的两种SDI视频方案(GTX+外接芯片) |

| ||

相关帖子

|

||

关闭

站长推荐

站长推荐 /2

/2

ICP经营许可证 苏B2-20140176 苏ICP备14012660号-2 苏州灵动帧格网络科技有限公司 版权所有.

Powered by Discuz! X3.4

Copyright © 2001-2020, Tencent Cloud.

发表于 2021-2-4 21:08:39

发表于 2021-2-4 21:08:39