PS和PL间的通信方式有四种:

1、EMIO方式,如上图标1处所示,相当于把PS外设的引脚内部连接到FPGA上,总共有192个EMIO可以作为GPIO连接到PL部分,其中128个为PS输出到PL部分,64个为PL输出到PS部分,这个只适用于低速通信的场合。

2、AXI_GP接口方式,如上图标2处所示,总共有四个通信接口,总线宽度都是32位,包括两个AXI_GP主设备接口(PS为主设备)和两个AXI_GP从设备接口(PS为从设备),主要用在一般速率或者通用情况下的互连通信。

3、AXI_HP接口,如上图标3处所示,总共有四个通信接口,总线宽度可以配置为32位或者64位,都是高性能/带宽的AXI3.0标准的接口,PL为主设备发起访问,主要用于PL访问PS侧的存储器,包括DDR内存和片内RAM, 主要用在速率要求比较高的情况下的PS和PL通信。

4、AXI_ACP接口(加速器一致性端口),如上图标4处所示,总线宽度是64位,PL为主设备发起访问,通过该接口,PL可以直接访问PS的cache,同时也可以第一时间将逻辑加速运算结果送至cache中,特点是有很低的延迟,适合做专用指令加速器模块的通信接口。

以上对PS和PL间的可能的通信方式了解后,我们以创龙科技提供的tl-axi-gpio-led-demo例程进行实验,该例程在PL侧使用了一个AXI GPIO IP核,PS处理器通过上面介绍的AXI_GP接口来访问控制该GPIO IP,具体步骤如下:

1、拷贝创龙科技提供的第一张光盘的Demo\All-Programmable-SoC-demos\tl-axi-gpio-led-demo目录到一个工作目录,然后打开vivado2017.4工具的Tcl Console窗口,输入下面命令进入脚本所在目录,如cd C:/ tl-axi-gpio-led-demo/hw/src/scripts目录;然后执行vivado -mode batch -source tl_axi_gpio_led_project.tcl -tclargs tlz7x-easyevmxc7z020clg400-2,Tcl脚本执行完成后,在工程源码" hw \src\runs"目录下生成对应开发平台的Vivado工程。

2、进入Vivado工程所在的hw \src\runs路径,双击tl-axi-gpio_led.xpr文件打开工程。然后在工程界面左侧点击"IPINTEGRATOR -> Open Block Design"打开块图,双击块图中的AXIGPIO核框图后可以查看到设置GPIO Width为1位,点击块图中的"Address Editor"选项,可以查看到AXI GPIOIP核分配的地址为0x4120_0000,在PS端通过该地址用AXI接口控制IP核,如下图示:

3、参考第一张光盘的用户手册目录下的《3-1-2-基于TcL脚本生成xsdk工程及编译.pdf》文档,首先编译第2步打开的工程产生Bitstream,然后在Vivado的菜单栏"File -> Export -> Export Hardware…",弹出对话框中点击OK导出硬件描述文件,生成的文件位于工程目录的" hw \src\runs\tl_axi_gpio_led.sdk\tl_axi_gpio_led_wrapper.hdf"文件,将该文件拷贝到“\sw\baremetal_demo\src”目录下。

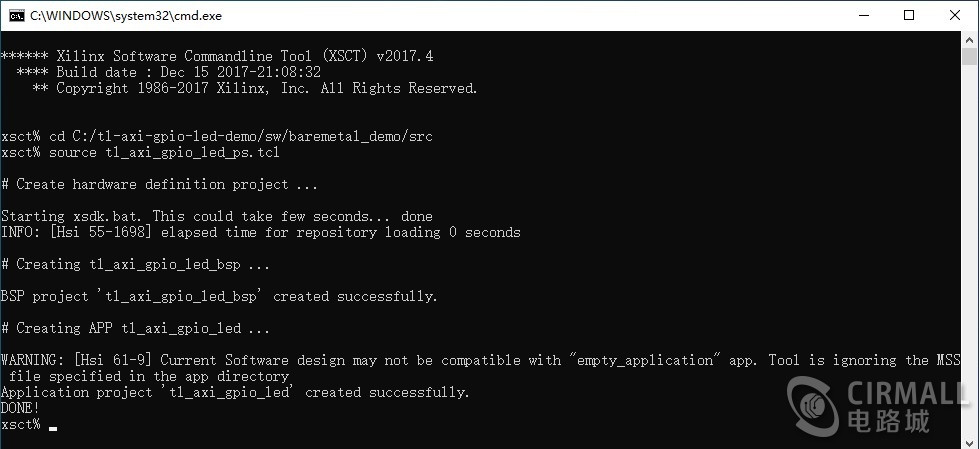

4、双击vivado2017.4安装目录下的"Xilinx\SDK\2017.4\bin\xsct.bat"文件将XSCT终端打开,在XSCT终端输入如下命令进入到脚本所在目录:cd C:/ tl-axi-gpio-led-demo/sw/baremetal_demo/src,在输入source tl_axi_gpio_led_ps.tcl命令生成xsdk工程,如下图示:

5、关闭XSCT终端,在双击vivado2017.4安装目录下的"Xilinx\SDK\2017.4\bin\ xsdk.bat "文件将Xilinx SDK工具打开,在弹出的Workspace选择界面中,点击"Browse…"按钮,选择需要打开的xsdk工程或者直接输入xsdk工程所在路径,如C:/ tl-axi-gpio-led-demo/sw/baremetal_demo/src/tl_axi_gpio_led.sdk。然后在SDK工具界面点”Window->Show View -> ProjectExplorer”调出工程浏览界面(如果有Welcom界面需要先关闭),然后就可以正常编译调试程序了。

6、实际测试,首先连接JTAG下载器到开发板上,然后把开发板的启动方式拨码开关拨码为010101(1~6 JTAG模式),最后打开电源开关给开发板上电,再在SDK工具界面先编译程序,然后下载FPGA bitstream后再下载PS程序,最后可以看到底板上的LED2在闪烁,具体操作视频如下所示:

/2

/2

/2

/2